NEW

YORK, June 19, 2024 /PRNewswire/ -- The global

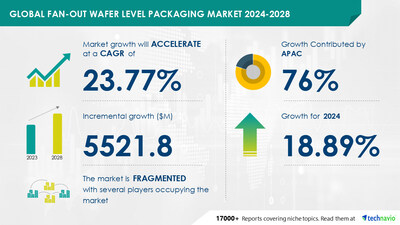

fan-out wafer level packaging market size is estimated to

grow by USD 5.52 billion from

2024-2028, according to Technavio. The market is estimated to grow

at a CAGR of over 23.77% during the forecast

period. Increased demand for compactly designed

electronics is driving market growth, with a trend

towards increasing adoption of semiconductor ics in

automobiles. However, increased production costs because of

warpage poses a challenge. Key market players include Amkor

Technology Inc., ASE Technology Holding Co. Ltd., Deca Technologies

Inc., Infineon Technologies AG, Jiangsu Changdian Technology Co.

Ltd., nepes Corp., Nordson Corp., NXP Semiconductors NV, Onto

Innovation Inc., Panasonic Holdings Corp., Powertech Technology

Inc., Renesas Electronics Corp., Singapore Semiconductor Industry

Association, SUSS MICROTEC SE, Taiwan Semiconductor Manufacturing

Co. Ltd., Unisem M Berhad, UTAC Holdings Ltd., Winbond Electronics

Corp., Yield Engineering Systems, and Yole Developpement SA.

Get a detailed analysis on regions, market

segments, customer landscape, and companies - Click for the

snapshot of this report

|

Forecast

period

|

2024-2028

|

|

Base Year

|

2023

|

|

Historic

Data

|

2018 - 2022

|

|

Segment

Covered

|

Technology (High

density and Standard density), Type (200 mm, 300 mm, and Panel),

and Geography (APAC, North America, Europe, South America, and

Middle East and Africa)

|

|

Region

Covered

|

APAC, North America,

Europe, South America, and Middle East and Africa

|

|

Key companies

profiled

|

Amkor Technology Inc.,

ASE Technology Holding Co. Ltd., Deca Technologies Inc., Infineon

Technologies AG, Jiangsu Changdian Technology Co. Ltd., nepes

Corp., Nordson Corp., NXP Semiconductors NV, Onto Innovation Inc.,

Panasonic Holdings Corp., Powertech Technology Inc., Renesas

Electronics Corp., Singapore Semiconductor Industry Association,

SUSS MICROTEC SE, Taiwan Semiconductor Manufacturing Co. Ltd.,

Unisem M Berhad, UTAC Holdings Ltd., Winbond Electronics Corp.,

Yield Engineering Systems, and Yole Developpement SA

|

Key Market Trends Fueling Growth

The automotive industry's shift from mechanical and hydraulic

systems to electronic or hybrid alternatives, driven by the rise of

autonomous cars, is fueling the demand for semiconductor ICs and

sensors. This trend is leading to the increased adoption of FOWLP

(Fan-Out Wafer Level Packaging) technology in the automotive

sector. Major car manufacturers like Audi, General Motors, and

Tesla are investing in ICs and sensors for advanced driver

assistance systems (ADAS) and autonomous vehicles. FOWLP offers

high material density, greater I/O points, and improved

reliability, making it the preferred packaging solution for

automotive ICs. Safety regulations and the need for smart

automotive solutions are also driving the demand for MEMS sensors,

further boosting the FOWLP market.

The Fan-Out Wafer Level Packaging (FO-WLP) market is

experiencing significant growth, driven by the increasing demand

for smaller, more efficient semiconductor devices. Memory and logic

semiconductors are the primary applications for FO-WLP technology.

The use of FO-WLP in power management and sensor applications is

also on the rise. The trend towards higher integration and

miniaturization in electronics is fueling the adoption of FO-WLP.

The technology offers several advantages, including reduced power

consumption, improved reliability, and increased design

flexibility. The future looks bright for FO-WLP, with continued

innovation and advancements expected in this dynamic

market.

Research report provides comprehensive data on

impact of trend. For more details- Download a Sample

Report

Market Challenges

- The FOWLP market faces challenges due to warpage issues, which

increase production costs. Warpage is a distortion in the molded

part's surface, leading to wafer deformation and wastage.

Differential shrinkage, thermal expansion mismatches, and

post-processing steps are common causes. These issues result in

higher manufacturing and packaging costs for ICs, potentially

hindering market growth.

- The Fan-Out Wafer Level Packaging (FO-WLP) market faces several

challenges. One challenge is the complexity of the technology,

which requires precise chip placement and interconnect design.

Another challenge is the high cost of FO-WLP compared to

traditional packaging methods. Additionally, the need for high

yield and reliability in FO-WLP is crucial for mass production.

Furthermore, the integration of different materials and processes

in FO-WLP can be difficult, requiring advanced manufacturing

techniques. Lastly, the increasing demand for smaller form factors

and higher performance in electronic devices puts pressure on the

FO-WLP industry to continuously innovate and improve.

For more insights on driver and

challenges - Download a Sample Report

Segment Overview

This fan-out wafer level packaging market report extensively

covers market segmentation by

- Technology

- 1.1 High density

- 1.2 Standard density

- Type

- 2.1 200 mm

- 2.2 300 mm

- 2.3 Panel

- Geography

- 3.1 APAC

- 3.2 North America

- 3.3 Europe

- 3.4 South America

- 3.5 Middle East and

Africa

1.1 High density- The Fan-Out Wafer Level Packaging

(FO-WLP) market is experiencing significant growth due to the

increasing demand for miniaturization and higher integration in

semiconductor devices. FO-WLP technology enables the direct

connection of dies to the substrate, reducing the number of

interconnects and improving overall performance. Companies such as

Samsung, Micron, and SK Hynix are leading the market with their

innovative FO-WLP solutions. This technology is particularly

beneficial for memory and logic applications, leading to its

widespread adoption in the consumer electronics and automotive

industries.

For more information on market segmentation with

geographical analysis including forecast (2024-2028) and historic

data (2018 - 2022) - Download a Sample Report

Research Analysis

The Fan-Out Wafer Level Packaging (FO-WLP) market is

experiencing significant growth in various sectors, including

consumer electronics and advanced electronics. FO-WLP is a

semiconductor-based technology that enables footprint-sensitive

devices, such as smartphones, smartwatches, and laptops, to

incorporate high-performing ICs with minimal increase in size and

weight. This technology utilizes advanced packaging methods, such

as PoP (Package-on-Package) and memory-on-logic solutions, to

enhance the functionality of consumer electronics. FO-WLP also

addresses thermal issues by employing wafer-level packaging and

wafer-level processes. The IC packaging technology reduces

manufacturing costs and enables heterogeneous integration and panel

level technology in ultra-thin portable devices. FO-WLP is

revolutionizing the consumer electronics sector by enabling the

production of high-performing, compact devices.

Market Research Overview

The Fan-Out Wafer Level Packaging (FO-WLP) market refers to the

technology and process of integrating various semiconductor devices

onto a single wafer using wafer-level packaging techniques. This

packaging method offers several advantages such as reduced

interconnect resistance, improved reliability, and enhanced system

performance. The FO-WLP market caters to various applications

including memory, logic, and sensor technologies. The technology is

gaining popularity due to the increasing demand for

miniaturization, higher integration density, and the need for

advanced packaging solutions in the electronics industry. The

market is expected to grow significantly in the coming years due to

the increasing adoption of FO-WLP in advanced semiconductor

applications. The process involves various techniques such as

redistribution layer (RDL) formation, wafer bonding, and final

packaging. The market is driven by factors such as the increasing

demand for high-performance and power-efficient semiconductor

devices, the miniaturization trend in the electronics industry, and

the growing adoption of advanced packaging solutions.

Table of Contents:

1 Executive Summary

2 Market Landscape

3 Market Sizing

4 Historic Market Size

5 Five Forces Analysis

6 Market Segmentation

- Technology

-

- High Density

- Standard Density

- Type

-

- Geography

-

- APAC

- North America

- Europe

- South America

- Middle East And Africa

7 Customer Landscape

8 Geographic Landscape

9 Drivers, Challenges, and Trends

10 Company Landscape

11 Company Analysis

12 Appendix

About Technavio

Technavio is a leading global technology research and advisory

company. Their research and analysis focuses on emerging market

trends and provides actionable insights to help businesses identify

market opportunities and develop effective strategies to optimize

their market positions.

With over 500 specialized analysts, Technavio's report library

consists of more than 17,000 reports and counting, covering 800

technologies, spanning across 50 countries. Their client base

consists of enterprises of all sizes, including more than 100

Fortune 500 companies. This growing client base relies on

Technavio's comprehensive coverage, extensive research, and

actionable market insights to identify opportunities in existing

and potential markets and assess their competitive positions within

changing market scenarios.

Contacts

Technavio Research

Jesse Maida

Media & Marketing Executive

US: +1 844 364 1100

UK: +44 203 893 3200

Email: media@technavio.com

Website: www.technavio.com/

View original content to download

multimedia:https://www.prnewswire.com/news-releases/fan-out-wafer-level-packaging-market-size-is-set-to-grow-by-usd-5-52-billion-from-2024-2028--increased-demand-for-compactly-designed-electronics-to-boost-the-market-growth-technavio-302176433.html

View original content to download

multimedia:https://www.prnewswire.com/news-releases/fan-out-wafer-level-packaging-market-size-is-set-to-grow-by-usd-5-52-billion-from-2024-2028--increased-demand-for-compactly-designed-electronics-to-boost-the-market-growth-technavio-302176433.html

SOURCE Technavio