NXP Semiconductors Accelerates Design Cycle Using New Cadence Encounter Digital Implementation System for Industry's First 45nm

May 18 2009 - 3:01AM

Marketwired

Cadence Design Systems, Inc. (NASDAQ: CDNS), the leader in global

design innovation, announced today that NXP Semiconductors utilized

the new Cadenceďż˝ Encounterďż˝ Digital Implementation System (EDI

System), and its seamless design-for-manufacturing (DFM)

technologies to ensure reliable production of its advanced

45-nanometer PNX85500 digital TV processor chip with a significant

acceleration in productivity. The integrated, front-to-back EDI

System, with native DFM analysis and optimization, and Encounter

Timing System, provided the performance and accuracy necessary for

rapid signoff of the next-generation HDTV processor, enabling NXP

to quickly achieve volume production of the chip.

The PNX85500, from NXP's Home Business Unit, is the industry's

first 45-nanometer digital TV processor, delivering an

unprecedented viewing experience. It supports switching from analog

to digital, SD to HD and broadcast to networked TV with a global

single-chip TV platform. The EDI System enabled this complex

single-chip integration at 45 nanometers, consolidating the

features and functionality of two 90-nanometer chips to create the

area- and performance-efficient design layout, leading to

unparalleled picture quality.

"We had to meet an aggressive timeline for the PNX85500, since

the whole world is making a digital TV switchover," said Barry

Dennington, senior vice president of Design Technology at NXP

Semiconductors. "The scalable performance of the multi-CPU

backplane and the completeness of EDI System solution feature-set

meant we could stay in a single design environment from start to

finish. These performance and productivity advantages, coupled with

EDI System's native DFM optimization capabilities, and built-in

timing and signal integrity signoff, helped achieve a significant

improvement in overall turnaround time and time-to-market for our

design."

EDI System features a silicon-proven Litho Physical Analyzer and

CMP Predictor that can ameliorate 45-nanometer manufacturability

issues early in the design flow, enabling fast and predictable

design convergence. Combined with the industry-leading litho-driven

Cadence NanoRouteďż˝ Router, this reduced the need for post-GDSII DFM

optimization, further accelerating design time. The Encounter

Timing System is a complete and integrated advanced signoff

environment, enabling faster optimization, debug, statistical

analysis, and final verification of designs for timing, signal

integrity, and variability.

"We are excited to have yet another key collaborator success

using our new EDI System in production for advanced process nodes,"

said Dr. Chi-Ping Hsu, senior vice president of the Implementation

Products Group at Cadence. "This new system has been successfully

adopted by multiple worldwide customers and providing performance

and productivity advantages across the board. EDI System brings

customers a single scalable design environment for high performance

and quality design closure, with low-power, mixed-signal and

advanced node capabilities."

The Encounter Digital Implementation System is a configurable

and extensible high-performance, high-capacity, scalable design

solution uniquely delivering flat and hierarchical design closure

and signoff analysis, as well as low-power, advanced node and

mixed-signal design capabilities. Cadence DFM technologies are

seamlessly interwoven with the Encounter Digital Implementation

System, enabling early identification, analysis and repair of

yield-limiting design challenges. The system delivers superior

results and interoperability with package, logic and custom IC

design environments.

About Cadence

Cadence enables global electronic design innovation and plays an

essential role in the creation of today's integrated circuits and

electronics. Customers use Cadence software and hardware,

methodologies, and services to design and verify advanced

semiconductors, consumer electronics, networking and

telecommunications equipment, and computer systems. The company is

headquartered in San Jose, Calif., with sales offices, design

centers, and research facilities around the world to serve the

global electronics industry. More information about the company,

its products, and services is available at www.cadence.com.

Cadence, Encounter and the Cadence logo are registered

trademarks of Cadence Design Systems, Inc. in the United States and

other countries.

All other trademarks are the property of their respective

owners.

Add to Digg Bookmark with del.icio.us Add to Newsvine

For more information, please contact: Dan Holden Cadence Design

Systems, Inc. 408-944-7457 holden@cadence.com

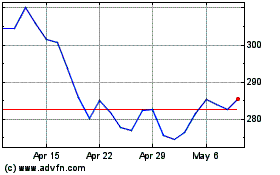

Cadence Design Systems (NASDAQ:CDNS)

Historical Stock Chart

From Sep 2024 to Oct 2024

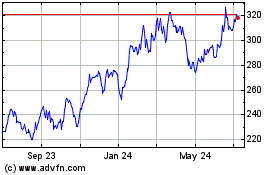

Cadence Design Systems (NASDAQ:CDNS)

Historical Stock Chart

From Oct 2023 to Oct 2024