Neuer 3Dblox 2.0 und Errungenschaften der

3DFabric Alliance werden beim 2023 OIP Ecosystem Forum im Detail

vorgestellt

TSMC (TSE: 2330, NYSE: TSM) kündigte heute auf dem TSMC 2023 OIP

Ecosystem Forum den neuen offenen 3Dblox 2.0-Standard sowie

wichtige Errungenschaften seiner Open Innovation Platform® (OIP)

3DFabric Alliance an. 3Dblox 2.0 bietet eine frühe

3D-IC-Designfähigkeit, die darauf abzielt, die Designeffizienz

erheblich zu steigern. Die 3DFabric Alliance setzt weiterhin auf

die Integration von Speicher, Substrat, Test, Fertigung und

Packaging. TSMC treibt die Innovation von 3D-IC weiter voran und

macht seine umfassenden 3D-Silizium-Stacking- und

Advanced-Packaging-Technologien für jeden Kunden zugänglicher.

„Angesichts der zunehmenden Akzeptanz der Branche von 3D-IC und

Innovationen auf Systemebene ist die Notwendigkeit einer

branchenweiten Zusammenarbeit heute noch wichtiger als vor 15

Jahren, als wir OIP gestartet haben“, sagte Dr. L.C. Lu,

TSMC-Fellow und Vice President des Geschäftsbereichs Design und

Technologieplattform. „Während unsere Zusammenarbeit mit den

Partnern des OIP-Ökosystems sich weiterhin gut entwickelt,

befähigen wir Kunden, die führenden Prozess- und

3DFabric-Technologien von TSMC zu nutzen, um ein v�llig neues

Leistungsniveau und eine h�here Energieeffizienz für KI der

nächsten Generation, Hochleistungsrechnen (HPC) und mobile

Anwendungen zu erreichen.“

„Wir arbeiten eng mit TSMC an fortschrittlicher

3D-Packaging-Technologie zusammen, die es den nächsten

MI300-Beschleunigern von AMD erm�glicht, branchenführende Leistung,

Speicherplatz und Bandbreite für KI- und Supercomputing-Workloads

zu bieten“, sagte Mark Fuselier, Senior Vice President für

Technologie und Produktentwicklung bei AMD. „Zusammen mit den

Partnern der 3DFabric Alliance hat TSMC ein umfassendes

3Dblox-Ökosystem entwickelt, das es AMD erm�glicht hat, die

Markteinführungszeit für unser 3D-Chiplet-Produktportfolio zu

verkürzen.“

3Dblox 2.0 Der im letzten Jahr eingeführte offene

Standard 3Dblox zielt darauf ab, 3D-IC-Designl�sungen für die

Halbleiterindustrie zu modularisieren und zu optimieren. Durch die

Beiträge des gr�ßten Ökosystems an Unternehmen ist 3Dblox zum

entscheidenden Design-Enabler für die zukünftige Entwicklung von

3D-IC geworden.

Der neue, heute eingeführte 3Dblox 2.0 erm�glicht die Erkundung

von 3D-Architekturen mit einer innovativen frühzeitigen

Designl�sung für Stromverbrauch- und thermische

Machbarkeitsstudien. Erstmals in der Branche kann der Entwickler

nun Stromdomänenspezifikationen und physikalische 3D-Konstruktionen

in einer ganzheitlichen Umgebung zusammenführen und Strom- und

Thermalsimulationen für das gesamte 3D-System durchführen. 3Dblox

2.0 unterstützt auch Funktionen zur Wiederverwendung von

Chiplet-Designs, wie beispielsweise die Spiegelung von Chiplets, um

die Designproduktivität weiter zu verbessern.

3Dblox 2.0 hat die Unterstützung wichtiger EDA-Partner gewonnen,

was die Entwicklung von Designl�sungen erlaubt, die alle

3DFabric-Angebote von TSMC vollständig unterstützen. Die

umfassenden Designl�sungen bieten Entwicklern entscheidende

Einblicke, um frühzeitige Designentscheidungen zu treffen und

beschleunigen den Designprozess von der Architektur bis zur

endgültigen Implementierung.

TSMC hat auch das 3Dblox-Komitee ins Leben gerufen, das als

unabhängige Standardgruppe organisiert ist und das Ziel hat, eine

branchenweite Spezifikation zu erstellen, die die Systemgestaltung

mit Chiplets von beliebigen Anbietern erm�glicht. Das Komitee

arbeitet mit wichtigen Mitgliedern wie Ansys, Cadence, Siemens und

Synopsys zusammen und verfügt über zehn technische Arbeitsgruppen

zu verschiedenen Themen. Es schlägt Verbesserungen der

Spezifikationen vor und sorgt für die Aufrechterhaltung der

Interoperabilität von EDA-Tools. Entwickler k�nnen die neuesten

3Dblox-Spezifikationen nunmehr von der Website 3dblox.org

herunterladen und mehr Informationen über 3Dblox und die

Tool-Implementierung durch EDA-Partner finden.

Errungenschaften der 3DFabric Alliance Als die ihrer Art

nach erste Allianz in der Halbleiterindustrie ist die 3DFabric

Alliance von TSMC im letzten Jahr enorm gewachsen und arbeitet

daran, Kunden eine breite Palette bewährter L�sungen und

Dienstleistungen für Halbleiterdesign, Speichermodule,

Substrattechnologie, Tests, Fertigung und Packaging

bereitzustellen. Das Unternehmen hat nun 21 3DFabric

Alliance-Partner in der Branche, mit denen es Innovationsarbeit

betreibt.

Kooperation bei Speichern: Generative KI und Anwendungen im

Zusammenhang mit großen Sprachmodellen erfordern mehr SRAM-Speicher

und eine h�here DRAM-Speicherbandbreite. Um diese Anforderungen zu

erfüllen, hat TSMC eng mit seinen wichtigen Speicherpartnern,

einschließlich Micron, Samsung Memory und SK hynix,

zusammengearbeitet, um das rasche Wachstum von HBM3 und HBM3e

voranzutreiben und generative KI-Systeme zu verbessern, indem mehr

Speicherkapazität bereitgestellt wird.

Kooperation bei Substraten: TSMC hat erfolgreich mit den

Substratpartnern IBIDEN und UMTC zusammengearbeitet, um eine

Substratdesign-Technikdatei zu definieren, die das automatische

Routing von Substraten für erhebliche Effizienz- und

Produktivitätssteigerungen erleichtert. Das Unternehmen hat eine

dreifache Zusammenarbeit mit Substrat- und EDA-Partnern initiiert,

um eine zehnfache Produktivitätssteigerung durch automatisches

Substrat-Routing zu erreichen. Die Zusammenarbeit beinhaltet auch

Design-for-Manufacturing (DFM)-Verbesserungsregeln, um Hotspots in

der Substratkonstruktion zu reduzieren.

Kooperation bei Tests: TSMC arbeitet eng mit Partnern für

automatische Testausrüstung (ATE) wie Advantest und Teradyne

zusammen, um verschiedene Herausforderungen bei 3D-Tests zu l�sen

und so den Ausbeuteverlust zu reduzieren und die Effizienz der

Stromversorgung für Chiplet-Tests zu verbessern. Um einen

Hochgeschwindigkeitstestzugriff für 3D-Stack-Tests über die

funktionale Schnittstelle zu demonstrieren, arbeitet TSMC mit

Synopsys und ATE-Partnern an einem Silizium-Demonstrator, um das

Ziel einer 10-fachen Steigerung der Testproduktivität zu erreichen.

Das Unternehmen arbeitet auch mit allen Design-for-Test

(DFT)-EDA-Partnern zusammen, um effektive und effiziente

Schnittstellentests zu gewährleisten.

Über die TSMC Open Innovation Platform (OIP) TSMC hat die

Open Innovation Platform im Jahr 2008 ins Leben gerufen, um

Designbarrieren abzubauen und die schnelle Umsetzung von

Innovationen in der Halbleiter-Design-Community zu f�rdern, indem

das kreative Denken von Kunden und Partnern zusammengeführt wird.

Dabei vereint sie das Ziel, die Designzeit, die Zeit bis zur

Serienreife, die Zeit bis zur Markteinführung und letztendlich die

Zeit bis zum Umsatz zu verkürzen. Die TSMC OIP bietet die

umfassendsten Design-Ökosystem-Allianzprogramme, an denen

branchenführende EDA-, Bibliotheks-, IP-, Cloud- und

Design-Service-Partner teilnehmen. TSMC hat seit der Gründung des

Unternehmens eng mit diesen Ökosystempartnern zusammengearbeitet

und erweitert seine Bibliotheken und sein Silizium-IP-Portfolio auf

mehr als 70.000 IP-Titel und stellt seinen Kunden mehr als 46.000

Technologiedateien und über 3.300 Prozessdesign-Kits von 0,5 Mikron

bis 2 Nanometer zur Verfügung.

Über TSMC TSMC leistete bei seiner Gründung im Jahr 1987

Pionierarbeit für das Pure-Play-Foundry-Geschäftsmodell und ist

seither die weltweit führende reine Halbleiter-Foundry. Das

Unternehmen unterstützt ein florierendes Ökosystem globaler Kunden

und Partner mit branchenführenden Prozesstechnologien und einem

Portfolio von Design-Enablement-L�sungen, um Innovationen für die

globale Halbleiterindustrie zu erm�glichen. Mit globalen

Niederlassungen in Asien, Europa und Nordamerika ist TSMC ein

weltweit engagierter Corporate Citizen.

Im Jahr 2022 setzte TSMC 288 verschiedene Prozesstechnologien

ein und fertigte 12.698 Produkte für 532 Kunden, indem es eine

breite Palette an fortschrittlichen, spezialisierten

Packaging-Technologien anbot. Das Unternehmen hat seinen Hauptsitz

in Hsinchu, Taiwan. Weitere Informationen finden Sie unter

https://www.tsmc.com.

Die Ausgangssprache, in der der Originaltext ver�ffentlicht

wird, ist die offizielle und autorisierte Version. Übersetzungen

werden zur besseren Verständigung mitgeliefert. Nur die

Sprachversion, die im Original ver�ffentlicht wurde, ist

rechtsgültig. Gleichen Sie deshalb Übersetzungen mit der originalen

Sprachversion der Ver�ffentlichung ab.

Originalversion auf businesswire.com

ansehen: https://www.businesswire.com/news/home/20230927804962/de/

Pressesprecher TSMC: Wendell

Huang Vice President und CFO 886-3-505-5901

Ansprechpartner Medien: Nina

Kao Head of Public Relations 886-3-563-6688 ext.7125036 Mobilfunk:

886-988-239-163 nina_kao@tsmc.com

Tiffany Yang Public Relations Manager 1-408-382-7934

tiffanyy@tsmc.com

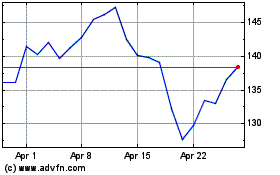

Taiwan Semiconductor Man... (NYSE:TSM)

Historical Stock Chart

From Apr 2024 to May 2024

Taiwan Semiconductor Man... (NYSE:TSM)

Historical Stock Chart

From May 2023 to May 2024