ASE & Cadence Deliver First System-in-Package EDA Solution Tailored for ASE’s High-Performance, Advanced IC Package Technol...

February 01 2018 - 1:56AM

Business Wire

Handles homogeneous and heterogeneous chip

integration with high-density packaging to enhance the efficiency

of chip and passive design optimization

Advanced Semiconductor Engineering, Inc. (ASE, TAIEX: 2311,

NYSE: ASX), and Cadence Design Systems, Inc. (NASDAQ: CDNS), today

announced they have collaborated to release a System-in-Package

(SiP) EDA solution that addresses the challenges of designing and

verifying Fan-Out Chip-on-Substrate (FOCoS) multi-die packages. The

solution consists of the SiP-id™ (System-in-Package - intelligent

design) design kit, an enhanced reference flow including IC

packaging and verification tools from Cadence, and a new

methodology that aggregates the requirements of wafer-, package-

and system-level design into a unified and automated flow. By

deploying the SiP-id™ methodology, designers can reduce design

iterations and greatly improve throughput as compared to existing

advanced packaging EDA tools, reducing the time needed to design

and verify ultra-complex SiP packages.

In today’s smart world, innovators are on the front line,

designing devices that pack greater functionality, generate higher

and faster performance, and consume lower power, all while being

integrated within shrinking space parameters. As a result, the role

of IC packaging in electronics has never been more important than

now. Technology has become an integral part of daily life, with

global proliferation of smartphones and wearables, and significant

application strides in artificial intelligence, autonomous vehicles

and the internet of things (IoT). These developments have created

immense opportunity for ASE to apply its SiP technology beyond

package level to module-, board- and system-level integration.

Previously, IC packaging engineers leveraged standard EDA design

tools coupled with a set of loosely defined rules to lay out their

packages. However, this approach has many limitations when

designing today’s advanced multi-die packages. To provide a more

holistic approach to the design and verification of SiP and

advanced fan- out packages, ASE and Cadence collaborated closely to

develop a design kit, methodology, and streamlined and automated

reference flow using enhanced Cadence® IC packaging and

verification tools, all tailored for ASE’s advanced IC package

technologies. In a typical use case with high-pin-count dies,

packaging engineers using SiP-id™ and the accompanying reference

flow and methodology were able to reduce time from more than six

hours to only 17 minutes, compared to existing tools with manual

operation.

“As the leader in System-in-Package technology, ASE has been

augmenting our design and manufacturing services by building a SiP

ecosystem with partners across the entire supply chain including

EDA providers,” said C. P. Hung, vice president, Corporate R&D,

ASE Group. “SiP-id™ is a prime example of the successful

collaboration between ASE and Cadence that achieved optimal results

through the mutual sharing of technology and experiences.

Ultimately, we aim to offer our customers a set of efficient EDA

tools to design more complex chips using ASE’s advanced package and

system-level technologies and help them speed up time to market,”

he added.

“More and more of our customers are looking at multi-die

advanced-package technologies to solve their next- generation

design challenges,” said Tom Beckley, senior vice president and

general manager of the Custom IC & PCB Group at Cadence.

“Advanced packaging extends Moore’s Law and plays directly into our

System Design Enablement strategy, so collaborating with ASE to

fulfill their vision for SiP is a natural fit for us. We expect the

results of this effort to mutually benefit Cadence and ASE

customers by providing a methodology optimized for SiP design.”

SiP-id™ is immediately available from ASE. For enquiries, please

email jennifer.yuen@aseus.com or visit

http://www.aseglobal.com/en/Technology/AdvancedTechnology.asp for

more information.

About Cadence

Cadence enables electronic systems and semiconductor companies

to create the innovative end products that are transforming the way

people live, work and play. Cadence software, hardware and

semiconductor IP are used by customers to deliver products to

market faster. The company’s System Design Enablement strategy

helps customers develop differentiated products—from chips to

boards to systems—in mobile, consumer, cloud datacenter,

automotive, aerospace, IoT, industrial and other market segments.

Cadence is listed as one of Fortune Magazine’s 100 Best Companies

to Work For. Learn more at cadence.com.

About The ASE Group

The ASE Group is among the leading providers of independent

semiconductor manufacturing services in assembly, test, materials

and design manufacturing. As a global leader geared towards meeting

the industry’s ever-growing needs for faster, smaller and higher

performance chips, the Group develops and offers a wide portfolio

of technology and solutions including IC test program design,

front-end engineering test, wafer probe, wafer bump, substrate

design and supply, wafer level package, flip chip,

system-in-package, final test and electronic manufacturing services

through USI Inc and its subsidiaries, members of the ASE Group. For

more information about the ASE Group, visit www.aseglobal.com or

twitter @asegroup_global.

Safe Harbor Notice

This press release contains “forward-looking statements” within

the meaning of Section 27A of the United States Securities Act of

1933, as amended, and Section 21E of the United States Securities

Exchange Act of 1934, as amended. Although these forward-looking

statements, which may include statements regarding our future

results of operations, financial condition or business prospects,

are based on our own information and information from other sources

we believe to be reliable, you should not place undue reliance on

these forward-looking statements, which apply only as of the date

of this press release. The words “anticipate,” “believe,”

“estimate,” “expect,” “intend,” “plan” and similar expressions, as

they relate to us, are intended to identify these forward-looking

statements in this press release. Our actual results of operations,

financial condition or business prospects may differ materially

from those expressed or implied in these forward-looking statements

for a variety of reasons, including risks associated with

cyclicality and market conditions in the semiconductor or

electronic industry; changes in our regulatory environment,

including our ability to comply with new or stricter environmental

regulations and to resolve environmental liabilities; demand for

the outsourced semiconductor packaging, testing and electronic

manufacturing services we offer and for such outsourced services

generally; the highly competitive semiconductor or manufacturing

industry we are involved in; our ability to introduce new

technologies in order to remain competitive; international business

activities; our business strategy; our future expansion plans and

capital expenditures; the uncertainties as to whether we can

complete the share exchange contemplated by a joint share exchange

agreement between Siliconware Precision Industries Co., Ltd. and

us; the strained relationship between the Republic of China and the

People’s Republic of China; general economic and political

conditions; the recent global economic crisis; possible disruptions

in commercial activities caused by natural or human-induced

disasters; fluctuations in foreign currency exchange rates; and

other factors. For a discussion of these risks and other factors,

please see the documents we file from time to time with the

Securities and Exchange Commission, including our 2016 Annual

Report on Form 20-F filed on April 21, 2017.

View source

version on businesswire.com: http://www.businesswire.com/news/home/20180131006496/en/

ASE GroupPatricia

MacLeodUS/EuropePatricia.MacLeod@aseus.comJennifer

YuenAsiaJennifer.Yuen@aseus.comorCadence

Newsroom408-944-7039newsroom@cadence.com

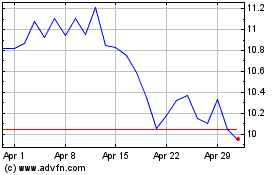

ASE Technology (NYSE:ASX)

Historical Stock Chart

From Aug 2024 to Sep 2024

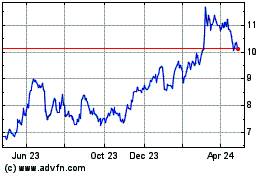

ASE Technology (NYSE:ASX)

Historical Stock Chart

From Sep 2023 to Sep 2024