Cadence Introduces 32/28-Nanometer Low-Power RTL-to-GDSII Silicon Realization Reference Flow for Common Platform Alliance

January 17 2011 - 8:00AM

Marketwired

Cadence Design Systems, Inc. (NASDAQ: CDNS), a leader in global

electronic design innovation, today introduced a qualified

32/28-nanometer reference flow targeting Common Platform™

technology. Cadence® collaborated closely with members of the

Common Platform alliance -- IBM, GLOBALFOUNDRIES, and Samsung

Electronics -- to develop a comprehensive flow from RTL synthesis

to GDSII signoff for the advanced node, low-power high-k metal gate

(HKMG) process technology.

This new Silicon Realization reference flow for the Common

Platform alliance is built around the Cadence end-to-end Encounter®

flow, including Encounter RTL Compiler, Encounter Test, Encounter

Conformal, the Encounter Digital Implementation System, Litho

Physical Analyzer, QRC Extractor, Encounter Timing System, and

Encounter Power System. It was validated using the 32/28-nanometer

ARM® low-power physical libraries, and employs the Common Power

Format (CPF)-enabled Cadence Low-Power Solution to maintain power

intent throughout the design process.

"We worked closely with Cadence to pursue an optimal design flow

that enables our mutual customers to create differentiated products

in 32/28-nanometer technology," said Gary Patton, vice president,

IBM Semiconductor Research and Development Center, on behalf of the

Common Platform alliance. "Cadence's Silicon Realization offering

of a fully optimized end-to-end design flow targeted to the Common

Platform 32/28-nanometer high-k metal gate technology marks our

mutual commitment to customer success."

The flow encompasses key foundry-validated technologies,

including physically aware synthesis, large-scale rapid design

exploration and physical prototyping, advanced timing and signal

integrity concurrent optimization with multi-mode and multi-corner

analysis and optimization, context-aware placement, advanced

OCV-aware clock tree synthesis, litho-aware routing, and in-design

signoff analysis for timing and power. In addition, concurrent

design for manufacturing (in-design DFM) technology is enabled on

demand to ensure manufacturability at 32 and 28 nanometers. The

Cadence Silicon Realization reference flow is fully optimized to

deliver significant power savings with utmost quality on all

counts, and offers time-to-market advantages for innovative

electronic designs targeted to the Common Platform alliance's 32/

28-nanometer process.

The recently announced Silicon Realization flow is the latest

Cadence offering supporting the EDA360 vision, which, among other

things, calls for industry-wide collaboration to address the

challenges of today's complex designs.

"Our close collaboration with the Common Platform partners

brings together silicon-proven tools, end-to-end flows and

methodologies as an aid to advanced designers looking to achieve

better predictability in design convergence, superior quality of

silicon and higher design productivity," said Chi-Ping Hsu, senior

vice president, Research and Development, Silicon Realization Group

at Cadence. "The close collaboration between Cadence and the Common

Platform alliance on advanced node, low-power design solutions for

Silicon Realization gives designers a fast track to silicon

success."

Solutions for 32/28-nanometer technology and other advanced

innovations will be presented at the Common Platform Technology

Forum on Jan. 18, 2011 at Santa Clara Convention Center. Forum

details can be found at www.commonplatform.com.

About Cadence Cadence enables global

electronic-design innovation and plays an essential role in the

creation of today's integrated circuits and electronics. Customers

use Cadence® software and hardware, methodologies, and services to

design and verify advanced semiconductors, consumer electronics,

networking and telecommunications equipment, and computer systems.

Cadence reported 2007 revenues of approximately $1.6 billion, and

has approximately 5,100 employees. The company is headquartered in

San Jose, Calif., with sales offices, design centers, and research

facilities around the world to serve the global electronics

industry. More information about the company, its products, and

services is available at www.cadence.com.

Cadence, Encounter and the Cadence logo are registered

trademarks of Cadence Design Systems, Inc., in the USA and other

countries. All other marks and names are the property of their

respective owners

Add to Digg Bookmark with del.icio.us Add to Newsvine

For more information, please contact: Dean Solov Cadence Design

Systems, Inc. 408-944-7226 dsolov@cadence.com

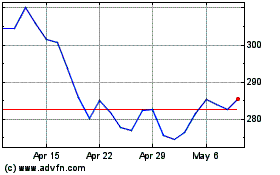

Cadence Design Systems (NASDAQ:CDNS)

Historical Stock Chart

From Sep 2024 to Oct 2024

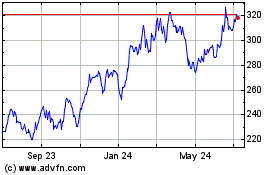

Cadence Design Systems (NASDAQ:CDNS)

Historical Stock Chart

From Oct 2023 to Oct 2024