Cadence Enhances Low-Power Solution Enabling More Predictable Power-Efficient Design

March 16 2009 - 8:00AM

Marketwired

Cadence Design Systems, Inc. (NASDAQ: CDNS), the leader in global

design innovation, announced today that the Cadenceďż˝ Low-Power

Solution has been enhanced to include support for new on-chip power

management schemes enabled by the recently ratified Si2 Common

Power Format (CPF) Version 1.1. The enhanced solution spans the

Cadence Encounterďż˝ digital implementation and logic design

technologies, as well as the Incisiveďż˝ functional verification and

system design and verification technologies. This upgraded solution

enables designers to more accurately model, analyze and debug power

management components targeted for integration into large

system-on-chip (SoC) designs. It includes macro modeling, seamless

multi-language support for IP integration and automated support of

metric-driven verification methodologies, such as those in the new

Cadence Incisive Enterprise Simulation Environment.

The power macro-modeling capability enables more accurate

characterization and analysis of power consumption within complex

SoC IP. Additionally, the Cadence Low-Power Solution is completely

generalized to enable a multitude of popular programming approaches

to IP block integration, and delivers automated low-power design

capabilities that extend well beyond implementation. These

enhancements enable the IP block or SoC to operate as designed and

within the power parameters required by the end application.

One proponent of the enhanced CPF-enabled solution is Virage

Logic. The company is consistently an early provider of advanced

technology solutions, and over the years has broadened the power

management capabilities of its SiWare(TM) Memory and SiWare(TM)

Logic product lines. By utilizing these products with the Cadence

Low-Power Solution, SoC designers can more accurately analyze the

benefits of the power management schemes in the context of their

full designs.

"As the semiconductor industry's trusted IP partner, we

recognize that support for macro modeling is essential for accurate

power modeling in today's complex memory sub-systems," said Brani

Buric, executive vice president of marketing and sales at Virage

Logic. "Our support of the Cadence Low-Power Solution enables us to

deliver accurate power modeling to our mutual customers, which in

turn enables them to develop complex, multifaceted SoCs that are

fully capable of optimizing the low-power capabilities embedded in

each IP block."

Another user of the CPF-enabled Cadence Low-Power Solution is

Sonics, a leading provider of intelligent interconnect solutions

that manage the on-chip communications in system-on-chip devices.

"Sonics provides our customers with low-power on-chip connectivity

solutions that allow a high degree of power control," said Jack

Browne, Senior Vice President of Marketing and Sales at Sonics.

"The inclusion of CPF 1.1 in Sonics products is an efficient way

for designers to leverage these low-power solutions as designers

integrate the IP back into their design flow."

Through the metric-driven Cadence Incisive Enterprise Simulation

suite, the Cadence Low-Power Solution now enables automated

assertion generation and automated low-power coverage for low-power

intent verification; voltage-aware simulation and voltage tracking;

full multi-language support for low-power verification; and

powerful new debug and visualization mechanisms.

"As customers innovate and create new methods to achieve more

power-efficient IC solutions, we are driven to innovate alongside

them," said Steve Carlson, vice president of Low-Power Solutions at

Cadence. "It is tremendously gratifying to work so closely with the

broad ecosystem of customers and collaborators to deploy these

solutions quickly into the design community."

About Cadence

Cadence enables global electronic design innovation and plays an

essential role in the creation of today's integrated circuits and

electronics. Customers use Cadence software and hardware,

methodologies, and services to design and verify advanced

semiconductors, consumer electronics, networking and

telecommunications equipment, and computer systems. The company is

headquartered in San Jose, Calif., with sales offices, design

centers, and research facilities around the world to serve the

global electronics industry. More information about the company,

its products, and services is available at www.cadence.com.

Cadence, Incisive and Encounter are registered trademarks and

the Cadence logo is a trademark of Cadence Design Systems, Inc. in

the United States and other countries. All other trademarks are the

property of their respective owners.

For more information, please contact: Dan Holden Cadence Design

Systems, Inc. 408-944-7457 holden@cadence.com

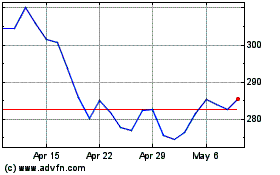

Cadence Design Systems (NASDAQ:CDNS)

Historical Stock Chart

From Oct 2024 to Nov 2024

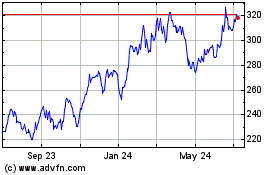

Cadence Design Systems (NASDAQ:CDNS)

Historical Stock Chart

From Nov 2023 to Nov 2024