Cadence Timing Signoff Tools Enable MaxLinear to Deliver Industry’s First 400Gbps PAM4 SoC on 16FF Process

December 10 2018 - 10:45AM

Business Wire

Cadence Quantus Extraction Solution and Tempus

Timing Signoff Solution provide faster convergence for on-time

tapeout and working silicon

Cadence Design Systems, Inc. (NASDAQ: CDNS) today announced that

MaxLinear, Inc., used Cadence® timing signoff tools to successfully

deliver the MxL935xx Telluride device, the industry’s first 400Gbps

PAM4 system on chip (SoC) using 16FF process technology. The

Cadence Quantus™ Extraction Solution and Tempus™ Timing Signoff

Solution were key enablers of the on-time delivery of working

silicon for MaxLinear. The Telluride device is the key component

for system vendors to be able to develop a 400Gbps optical

interconnect module in a compact form factor for intra-datacenter

applications with a transmission distance up to 2 kilometers.

For more information on the Quantus Extraction Solution, please

visit www.cadence.com/go/quantusmax. For more information on the

Tempus Timing Signoff Solution, please visit

www.cadence.com/go/tempusmax.

The Cadence timing signoff tools provided MaxLinear with the

ability to manage congestion throughout every stage of the design

flow, from placement to signoff, with a target of lowering design

density, allowing for high target utilization and cost tradeoffs

involving using more layers versus chip area. The Cadence timing

signoff tools provided MaxLinear with a trusted, reliable design

flow for fast runtimes, signoff accuracy, and first-pass

engineering change order (ECO) fixes to achieve on-time

tapeouts.

MaxLinear estimated that they were able to get 2X faster

multi-corner extraction runtimes versus single-corner runs and 3X

faster timing signoff flow with the Quantus and Tempus solutions.

MaxLinear was able to fix over 90 percent of hold violations with

Tempus ECO, which reduced their iterations to only 3-4 ECOs while

fixing across 18 timing views. The Tempus physically-aware ECO flow

helped MaxLinear to dramatically reduce the overall ECO cycle. The

key to the fastest convergence and reduction in iterations for

on-time tapeout was the fact that both the Innovus™ Implementation

System and Tempus ECO solution use the same signoff extraction and

STA engines for optimization and signoff.

“Managing heavily congested and high-speed SoC design throughout

the design flow with high-target utilization to reduce costs at

16FF node is a challenging task,” said Dr. Paolo Miliozzi, VP of

SoC Technology, MaxLinear. “We are able to deploy the full-flow

Cadence digital and signoff tool set including their Quantus,

Tempus, and Tempus ECO solutions for successful signoff and on-time

tapeout. Using these signoff engines, which are consistent with the

Cadence Innovus Implementation System for both extraction and

static timing analysis, ensured tight correlation and a reduction

in design iterations during signoff for quick design

convergence.”

MaxLinear used the Cadence full-flow digital solution including

Genus™ Synthesis Solution, Innovus Implementation system for place

and route, Quantus Extraction Solution and Tempus Timing Signoff

Solution. Cadence provides tightly integrated tools with unified

algorithms, engines and data models, as well as a common user

interface throughout the entire digital design process. A video

about the MaxLinear design experience is available at

www.cadence.com/go/maxlinearvideo.

About Cadence

Cadence enables electronic systems and semiconductor companies

to create the innovative end products that are transforming the way

people live, work and play. Cadence software, hardware and

semiconductor IP are used by customers to deliver products to

market faster. The company’s System Design Enablement strategy

helps customers develop differentiated products—from chips to

boards to systems—in mobile, consumer, cloud datacenter,

automotive, aerospace, IoT, industrial and other market segments.

Cadence is listed as one of Fortune Magazine's 100 Best Companies

to Work For. Learn more at www.cadence.com.

© 2018 Cadence Design Systems, Inc. All rights reserved

worldwide. Cadence, the Cadence logo and the other Cadence marks

found at www.cadence.com/go/trademarks are trademarks or

registered trademarks of Cadence Design Systems, Inc. All other

trademarks are the property of their respective owners.

View source

version on businesswire.com: https://www.businesswire.com/news/home/20181210005187/en/

For more information, please contact:Cadence

Newsroom408-944-7039newsroom@cadence.com

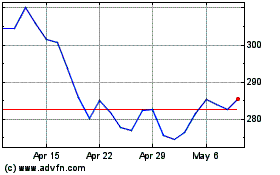

Cadence Design Systems (NASDAQ:CDNS)

Historical Stock Chart

From Mar 2024 to Apr 2024

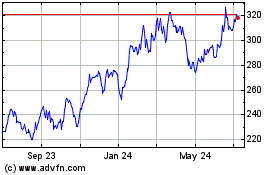

Cadence Design Systems (NASDAQ:CDNS)

Historical Stock Chart

From Apr 2023 to Apr 2024